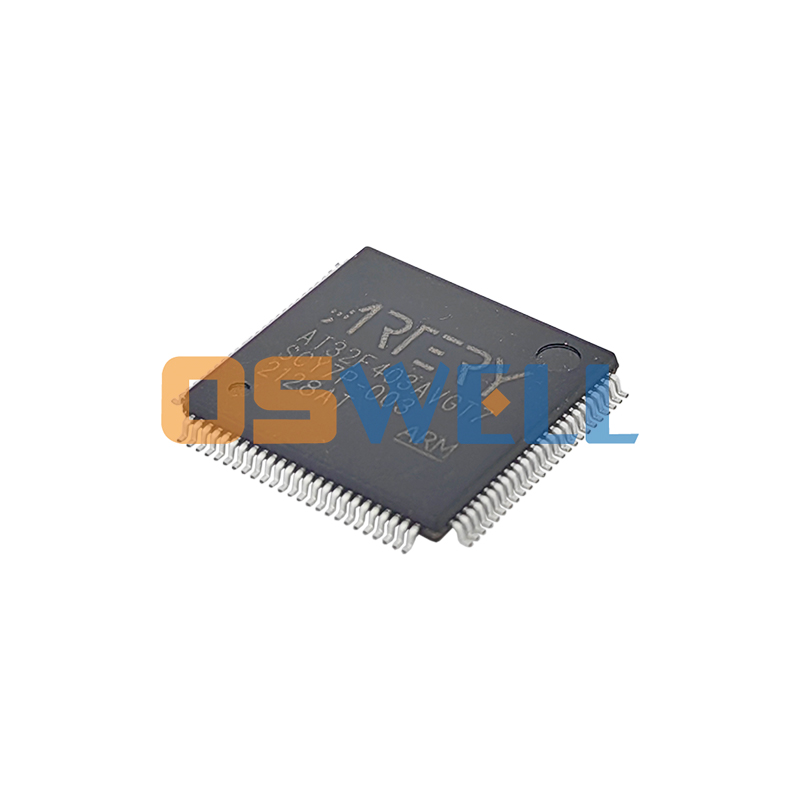

Chip di misurazione del microcontrollore AT32F403ARCT7

L'AT32F403A si basa sul core RISC a 32 bit ARM®Cortex® -M4 ad alte prestazioni fino a 240 MHz. Il core Cortex® -M4 presenta un'unità a virgola mobile (FPU) a precisione singola che supporta tutte le istruzioni di elaborazione dati a precisione singola ARM® e il tipo di dati. Implementa inoltre un set completo di istruzioni DSP e un'unità di protezione della memoria (MPU) che migliora la sicurezza delle applicazioni.

AT32F403ARCT7

L'AT32F403A incorpora memorie incorporate ad alta velocità (fino a 1024 KByte di memoria Flash interna, 96+128 KByte di SRAM), l'ampia SPI Flash esterna (capacità di indirizzamento fino a 16 MByte) e GPIO e periferiche migliorati collegati a due bus APB . Qualsiasi blocco della memoria Flash incorporata può essere protetto dalla “sLib”, che funziona come un'area di sicurezza con solo codice eseguibile.

L'AT32F403A offre tre ADC a 12 bit, due DAC a 12 bit, otto timer generici a 16 bit più due timer generici a 32 bit e fino a due timer PWM per il controllo del motore. Supporta interfacce di comunicazione standard e avanzate: fino a tre I2C, quattro SPI (tutti multiplexati come I2S), due SDIO, otto USART/UART, un USBFS e due CAN.

L'AT32F403A funziona nell'intervallo di temperatura da -40 a +105 °C, con alimentazione da 2,6 a 3,6 V. Un set completo di modalità di risparmio energetico consente la progettazione di applicazioni a bassa potenza.

L'AT32F403A offre dispositivi in diversi tipi di pacchetto. A seconda dei diversi pacchetti, il pin-to-pin è completamente compatibile tra i dispositivi, così come il software e le funzionalità. Sono inclusi solo diversi set di periferiche.

Caratteristiche:

Nucleo: CPU ARM® Cortex® -M4 a 32 bit con FPU

− Frequenza massima 240 MHz, con unità di protezione della memoria (MPU), moltiplicazione a ciclo singolo e divisione hardware

− Unità a virgola mobile (FPU) e

− Istruzioni DSP

Ricordi

− 256 KByte di memoria Flash interna

− sLib: parte configurabile di Flash principale impostata come area libreria con codice eseguibile ma protetto, non leggibile

− Interfaccia SPIM: Interfacciamento extra fino a 16 Mbyte della SPI Flash esterna (come istruzione/memoria dati)

− Fino a 96+128 KByte di SRAM

− Controller di memoria esterno (XMC) con bus dati a 16 bit. Supporta memorie PSRAM/NOR e NAND multiplexate

Pacchi

− LQFP64 10*10 mm